DVB-S2x

An ISRO RESPOND Project

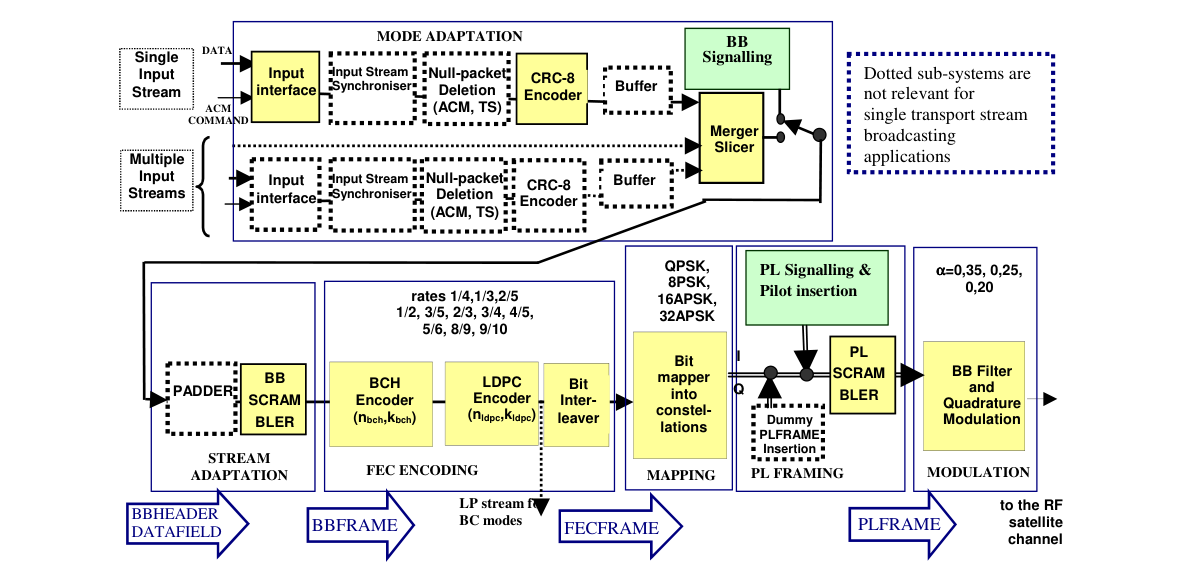

The prescribed architecture of the transmitter sub-system of DVB-S2x.

I contributed to the DVB-S2x project developed by the European Telecommunications Standards Institute (ETSI) for digital satellite television broadcasting. Successfully integrated a preliminary version of the transmitter subsystem, which showed promising results in simulations with MATLAB’s “DVB-S2 waveform generator” tool.

I was responsible for designing and implementing key transmitter components on an FPGA using Verilog, including:

- Cyclic Redundancy Check (CRC) 8

- BB Signalling and Slicer

- Zero Padder

- BB Scrambler

- Bose-Chaudhuri-Hocquhem (BCH) Encoder

I did this project during my third year (Aug 2023 to April 2024) at IIT Dharwad. The project was supervised by Prof. Rajsekhar V. Bhat, IIT Dharwad.